vivado工程Git版本控制

vivado工程Git版本控制

# vivado工程Git版本控制

为了更有效地维护FPGA项目,我决定采用Git进行版本控制。尽管我之前对Tcl脚本不太熟悉,而且Block Design的加入常常导致项目文件变得既多又大,我花了两天时间深入研究并掌握了这些内容。现在,我将我的发现记录下来,希望对初学者有所帮助。

# 1. 理解工程结构

在Vivado工程中,我们特别关注源代码、Block Design(BD)、XDC(约束文件)和IP(知识产权核)。这些文件通常存放在工程的`XXX.srcs`目录下。然而,由于Block Design生成的文件体积庞大,如果直接对这个目录进行版本控制,可能会失去版本控制的意义。

为了解决这个问题,我们可以将Block Design导出为Tcl脚本,并对 xxx.tcl文件进行版本控制。这样,我们只需要管理源代码、XDC文件、IP和TCL文件。

需要注意的是,如果项目中使用了sysgen、HLS等工具生成的IP,需要将这些IP的路径添加到工程中。这里不包括对自定义IP的版本控制说明。

还有一点很重要,导出的Tcl文件描述了Block Design中使用的自带库IP的参数和模块间的连接关系。在开始工作之前,确保所有使用的源代码文件和自定义IP都已准备就绪,然后通过source命令执行Tcl文件,即可在工程中创建Block Design文件。

# 2.STEP by STEP

我将以现有工程举例,修改其目录结构后提交到版本控制库。

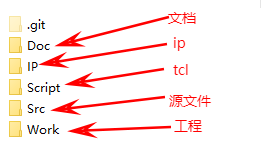

# 1、初始化Git仓库创建目录结构

其中Script放置bd脚本、工程脚本;Work中放置vivado工程,并且该目录设置ignore。

# 2、新建工程

1、到Work目录下建立vivado空工程

2、将源文件、约束拷贝到Src,将ip拷贝到IP,这里我将旧工程中的src拷贝过来了

3、添加src、ip路径(如果用到自定义的IP)

4、将原工程的block design保存到tcl,如果有多个,则分别保存

5、在新工程中打开Tcl Console, 移动到脚本的路径: cd E:/Proj_Path/Script

source design_2.tcl,会在新工程中创建block_design

6、不出意外的话新工程就建立完毕

# 3、代码提交

.gitignore 文件定义如下:

# Vivado-generated directories and files

*.jou

*.log

*.str

*.zip

*.xsim/

*.cache/

*.hw/

*.ip_user_files/

*.runs/

*.sim/

*.webtalk/

*.wdb

# Specific project files

*.dcp

*.xpr

*.xise

*.xisebak

*.bak

*.rpt

*.vcd

*.sysdef

# Simulation output

*.wcfg

*.wdb

# Build outputs

*.bit

*.bin

*.elf

*.mcs

# Miscellaneous

*.lock

Work

Proj

Bin/*

!Bin/do_tcl.bat

!Bin/Full_Bitstream.bif

!Bin/gen_bitbin.tcl

**/__pycache__

**/.idea

*.csv

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

上次更新: 2025/02/14, 14:21:56